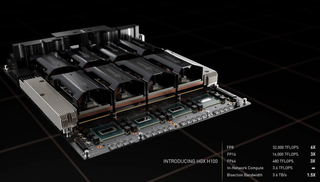

Важность технологий трёхмерной компоновки чипов подчёркивается создавшейся на рынке ускорителей вычислений ситуацией. «Узким местом» в случае с выпуском профильных компонентов NVIDIA стали возможности компании TSMC по упаковке и тестированию чипов с использованием метода CoWoS. Спрос на такие услуги вырос в три раза, и сейчас TSMC способна от силы удовлетворять потребность рынка на 80%, хотя к концу следующего года и обещает удвоить свои производственные мощности на Тайване.

Как поясняет Bloomberg, глава американского разработчика ПО для проектирования чипов Cadence Design Systems призвал местные компании и власти активнее вкладывать средства именно в технологии пространственной упаковки чипов. Используя спортивную терминологию, Анирудх Девган (Anirudh Devgan) заявил, что «шайба сейчас как раз находится на территории трёхмерной интеграции микросхем».

Источник изображения: NVIDIA

По его словам, для развития бизнеса по упаковке чипов не нужны предприятия по обработке кремниевых пластин, и власти США должны задуматься о поддержке данной отрасли промышленности. Финансовый директор Intel Дэвид Зинснер (David Zinsner) недавно подтвердил, что предприятия по упаковке чипов начинают быстрее приносить прибыль, чем обрабатывающие кремниевые пластины. В свою очередь, Cadence собирается претендовать на часть тех $52 млрд, которые власти США направят в ближайшие пять лет на поддержку национальной полупроводниковой отрасли.

Источник новости: overclockers.ru