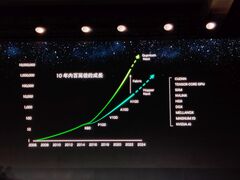

Современные чипы достигли рекордного уровня сложности, они вмещают более 50 млрд. транзисторов на площади больше 800 мм², поэтому разрабатывать их вручную уже не представляется возможным. Инструменты Electronic Design Automation (EDA) позволяют автоматизировать процесс разработки дизайна чипов, чтобы вмещать на минимальной площади максимум электронных схем без ущерба производительности.

Сегодня в данный процесс повсеместно вовлекаются алгоритмы машинного обучения. Synopsis предлагает свое решение DSO.ai, улучшающее EDA до 26% (подразумевается меньшее энергопотребление). Google рассказывала о разработке дизайна чипов с использованием алгоритмов Deep Reinforcement Learning еще весной 2020. Те же Cadence или Mentor (Siemens) предлагают схожие инструменты.

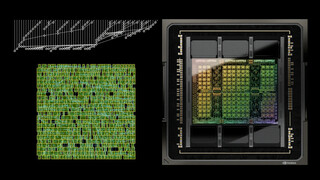

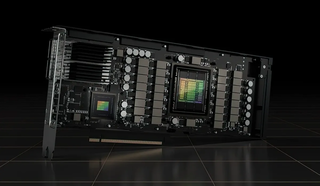

NVIDIA представила результаты исследования, которое использует метод обучения с подкреплением (reinforcement learning, RL) для автоматизированной разработки чипов. Дизайн H100 GPU на архитектуре Hopper использует 13.000 инстанций RL, если верить NVIDIA. К подобным частичным схемам на GPU относятся, например, сумматоры или шифраторы, они встречаются в большом количестве, и при автоматическом дизайне их можно реализовать намного более эффективно.

Алгоритмы машинного обучения с подкреплением пробуют различные расположения схем на кристалле, пытаясь найти оптимальную структуру после множества итераций. Помимо площади роль играют также задержки: чем крупнее область, тем выше будут задержки из-за длины интерконнекта.

NVIDIA сравнивает схему, созданную PrefixRL и стандартными инструментами EDA, при этом у PrefixRL можно видеть преимущество по всей кривой (соотношение площади и задержек, см. анимацию). 64-битный сумматор в результате удалось сделать на 25% меньше с площадью 31,4 мкм² и задержками 0,186 нс (см. график выше).

Конечно, NVIDIA не раскрывает все карты. Но с 50 млрд. транзисторов и выше (чип H100 GPU содержит целых 80 млрд.), не говоря уже о многочиповых дизайнах со 100 млрд. транзисторов, создавать дизайн чипов вручную уже не представляется возможным. Инструменты автоматического дизайна существуют многие годы, но с определенного уровня сложности требуется совершенно иной качественный подход.

Подобные инструменты требуют длительного и сложного процесса тренировки. В случае упомянутой сети PrefixRL на разработку 64-битного сумматора потребовалось около 32.000 часов GPU.

Источник новости: www.playground.ru