Издание Economic Daily уточняет, что деятельность TSMC по расширению своих мощностей, задействованных в упаковке передовых чипов, не ограничится возможным новым предприятием в Японии. В январе руководство компании подтвердило, что рассчитывает до конца этого года удвоить количество производственных линий, задействованных на операциях тестирования и упаковки чипов по методу CoWoS.

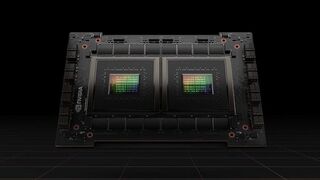

Источник изображения: NVIDIA

По данным китайских СМИ, в одном только технопарке Цзяи в ближайшие годы TSMC планирует построить шесть цехов по упаковке чипов с использованием методики CoWoS, и два первых цеха начнут возводиться уже в этом квартале. На соответствующие нужды TSMC в общей сложности готова потратить до $70 млрд. Хотя непосредственно корпуса двух первых предприятий будут готовы уже в следующем году, монтаж оборудования и его настройка займут время до 2027 года, как утверждают китайские источники.

Проблема нехватки мощностей по упаковке чипов методом CoWoS усложняется тем, что с каждым новым поколением компоновка флагманских чипов NVIDIA усложняется всё сильнее. Если в случае с H100 можно было с каждой кремниевой пластины получить до 28 чипов, то с выходом B100 это количество сократится до 16 чипов с пластины. Соответственно, производительность конвейера будет регулярно снижаться, и при растущем спросе это создаст дополнительные проблемы. По оценкам сторонних экспертов, если в этом году NVIDIA реализует 400 000 ускорителей H100, то B100 будут проданы тиражом от 500 до 600 тысяч штук. Компании TSMC потребуется ещё больше линий по упаковке таких чипов.

Источник новости: overclockers.ru