Представлен проект отдельного процессора под названием PyXL для выполнения байткода Python под девизом «No VM, No C, No JIT. Just PyXL and actual Python executed in silicon». Проект развивает инженер и разработчик Рон Ливне (Ron Livne), специализирующийся на оптимизации производительности и разработке аппаратных ускорителей.

Технические детали реализации проекта PyZX будут представлены 17 мая на конференции PyCon 2025. Авторы проекта рассматривают возможность открытия наработок проекта и создания самодостаточного ASIC‑чипа, но понимание ситуации по этим вопросам пока окончательно не определено.

Решение PyXL предназначено для ускорения выполнения кода на языке Python. Байткод Python напрямую выполняться чипом без JIT, интерпретации и виртуальных машин. Файлы на языке Python вначале транслируются в байткод CPython, после чего байткод преобразуется в специализированный набор инструкций PySM. Инструментарий для подготовки кода к выполнению при помощи чипа написан на Python и работает в стандартном окружении на базе немодицифированного CPython.

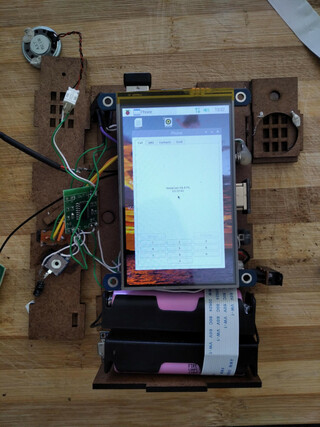

Реализация процессора PyXL разработана с нуля и оформлена на языке описания и моделирования электронных систем Verilog. Рабочий прототип процессора тестируется на платах с FPGA Zynq-7000.

В проведённых командой проекта тестах на обработку событий GPIO предложенное решение опережает решение на базе MicroPython и платы Pyboard в 30 раз — при выполнении тестового кода при помощи реализации PyXL, работающей с тактовой частотой 100 МГц, задержка обработки запроса GPIO (Roundtrip Latency) составила 480 нс, а при помощи MicroPython Pyboard (168MHz) — 14 741 нс.

Предполагается, что повышение тактовой частоты PyXL до уровня Pyboard позволит увеличить разрыв до 50 раз.

По информации OpenNET, при работе с GPIO на MicroPython при использовании платы PyBoard код на языке Python взаимодействует с аппаратными регистрами через промежуточные C‑функции, при этом сам Python-код выполняется в виртуальной машине.

В проекте PyXL байткод Python выполняется напрямую процессором и доступ к GPIO осуществляется без дополнительных прослоек и внешних вызовов. Архитектура PyXL использует использует конвейерную обработку (pipelining) и стек для хранения и обработки данных. Платформа сохраняет динамическую типизацию Python и не накладывает ограничений на типы переменных.

На текущем этапе развития проект PyXL находится на стадии рабочего прототипа, поддерживающего ограниченное подмножество языка Python и нацеленное на демонстрацию возможности эффективного аппаратного выполнения Python‑кода. Дальнейшее расширение функциональности PyXL планируют производить с учётом реальных потребностей автора, которые в основном сосредоточены на применении для встраиваемых систем и обработки информации в режиме реального времени.

Архитектура набора команд процессора PyXL спроектирована с оглядкой на структуру байткода CPython и его эффективную обработку на аппаратном уровне с учётом специфики, такой как динамическая обработка типов и динамическая диспетчеризация. ISA включает инструкции для манипуляции стеком, бинарные операции, операции сравнения и ветвления, возможности вызова функций и доступа к памяти.

Источник новости: habr.com