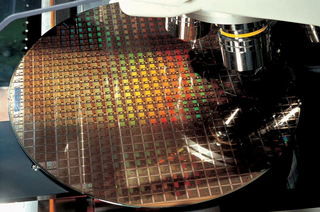

Intel представила несколько интересных достижений в области производства полупроводников на международной конференции по твердотельным схемам (ISSCC), продемонстрировав возможности долгожданной техпроцесса Intel 18A.

Отмечены значительные улучшения в плотности битовых ячеек SRAM. Система PowerVia в сочетании с транзисторами RibbonFET (GAA) лежит в основе техпроцесса Intel. Компания продемонстрировала значительный прогресс в разработке высокопроизводительных ячеек SRAM, добившись уменьшения площади с 0,03 мкм² в Intel 3 до 0,023 мкм² в Intel 18A.

Ячейки высокой плотности показали аналогичное улучшение, уменьшившись до 0,021 мкм². Эти достижения представляют собой коэффициенты масштабирования 0,77 и 0,88 соответственно, что является значительным прогрессом в технологии SRAM, которая когда-то считалась не подлежащей масштабированию.

Применение технологии PowerVia — это инновационный подход Intel к решению проблемы перепадов напряжения и помех в логических областях процессора. Используя схему «вокруг массива», Intel стратегически применяет PowerVia к элементам ввода-вывода, управления и декодирования, оптимизируя при этом конструкцию битовых ячеек без фронтального источника питания.

Плотность битов 38,1 Мбит/мм², достигнутая Intel 18A, обеспечивает компании сильные конкурентные позиции. В то время как TSMC сообщила о сопоставимых показателях для своего техпроцесса N2, комплексный подход Intel с использованием 18-нанометрового техпроцесса, сочетающего транзисторы PowerVia и GAA, может составить конкуренцию Smausng и TSMC в долгосрочной перспективе, чтобы конкурировать за клиентов премиум-класса, которых в настоящее время обслуживает TSMC, включая таких гигантов, как NVIDIA, Apple и AMD.

Источник новости: www.playground.ru